# **Quick Revision**

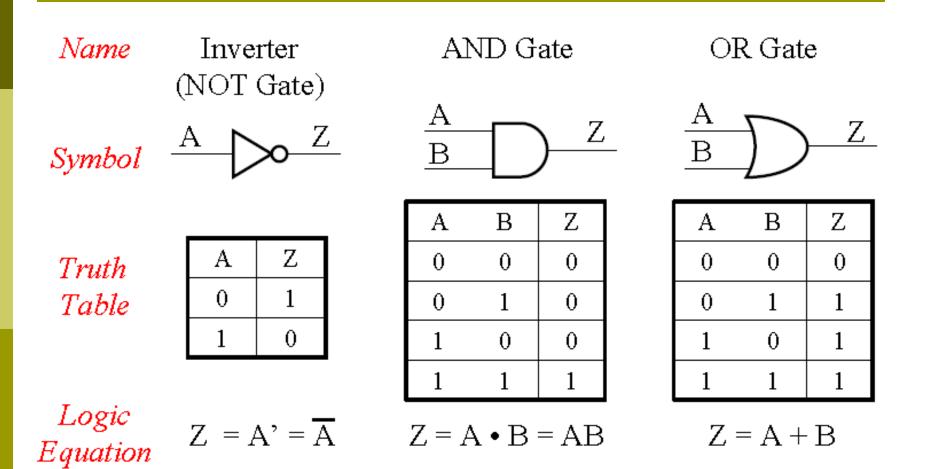

## **Elementary Logic Gates**

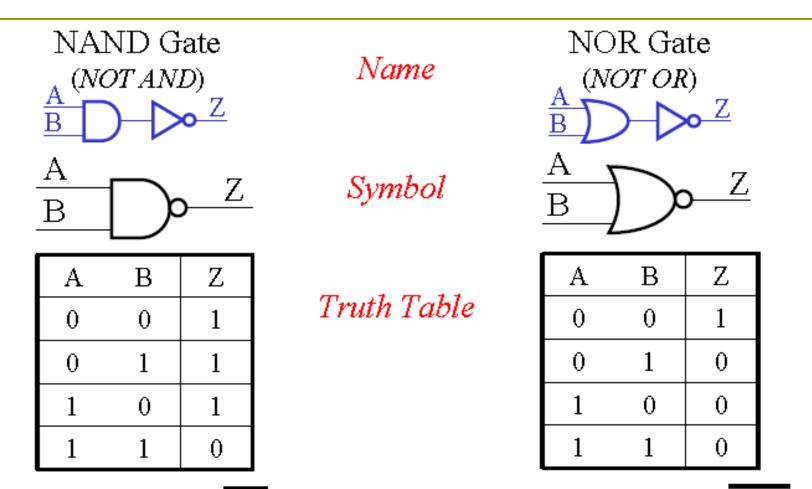

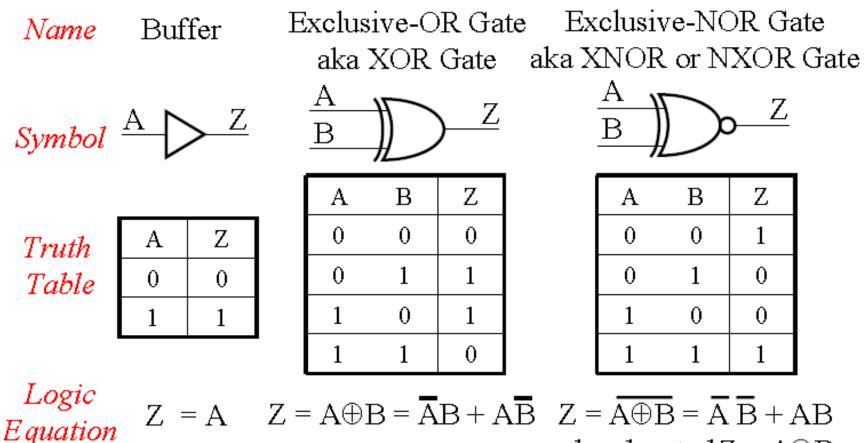

## **Other Elementary Logic Gates**

$Z = (A \bullet B)' = \overline{AB}$  Logic Equation  $Z = (A + B)' = \overline{A+B}$

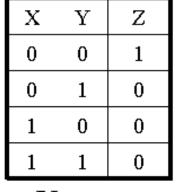

#### Using Truth Table to Prove theorem

• DeMorgan's Theorems

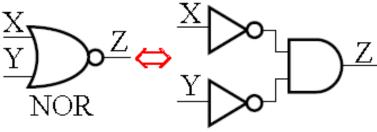

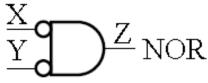

T8a:

$$(X+Y)' = X' \cdot Y'$$

a NOR gate is equivalent to an AND gate with inverted inputs

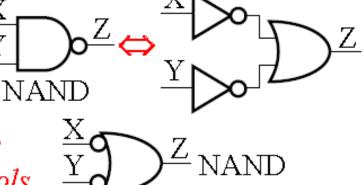

T8b:

$$(X \bullet Y)' = X' + Y'$$

a NAND gate is equivalent to an OR gate with inverted inputs

| X | Υ | Ζ |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

alternate logic symbols

## **Other Logic Gates**

also denoted  $Z = A \odot B$

## **Interesting Properties of XOR**

- Controlled inverter

- ≻X⊕0=X

- ≻X⊕1=X'

- XOR with one input inverted = XNOR

> X⊕Y'=X'⊕Y=(X⊕Y)'

- XNOR with one input inverted = XOR

> (X⊕Y')'=(X'⊕Y)'=X⊕Y

- Constant output

- ≻X⊕X=0

- ≻X⊕X'=1

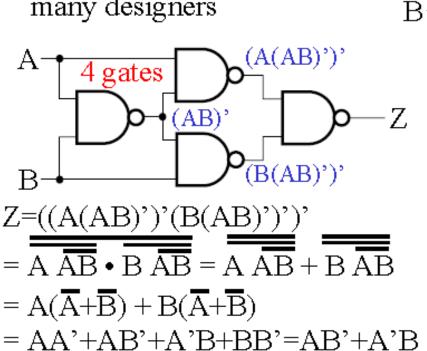

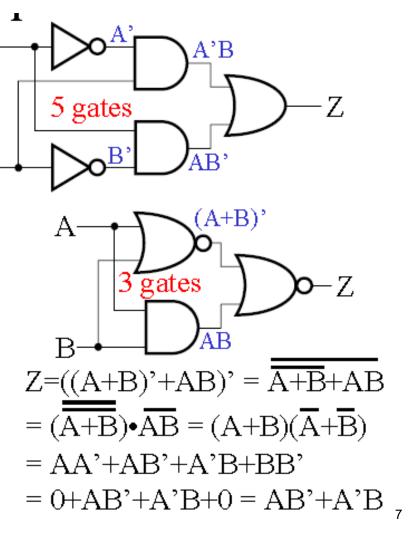

### **Exclusive-OR Implementation**

А

- Z=A'B+AB'

- XOR & XNOR not considered elementary logic gates by many designers

### **Gate-level Representation**

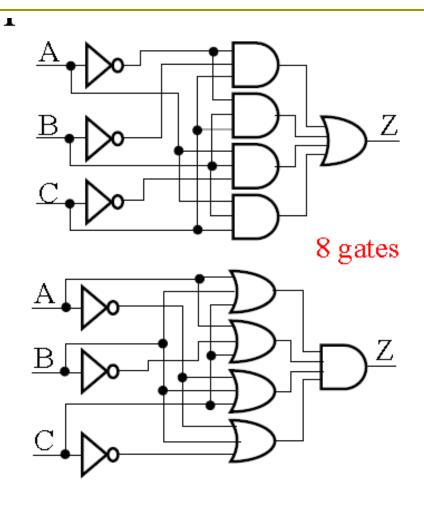

- SOP expressions ≻ AND-OR

- With inverters for complemented literals

Z=A'B'C+A'BC+ABC'+ABC

- ➤ aka 2-level AND-OR logic representation

- POS expressions ≻ OR-AND

- With inverters for complemented literals

Z=(A+B+C)•(A+B'+C) •(A'+B+C)•(A'+B+C')

- aka 2-level OR-AND logic representation

#### **Common Combinational Logic Circuits**

- Adders

- Subtraction typically via 2s complement addition

- Multiplexers

- N control signals select 1 of up to 2N inputs as output

- Demultiplexers

- N control signals select input to go to 1 of up to 2N outputs

- Decoders

- N inputs produce M outputs (typically M > N)

- Encoders

- N inputs produce M outputs (typically N > M)

- Converter (same as decoder or encoder)

- N inputs produce M outputs (typically N = M)

### **More Common Circuits**

#### Comparators

- Compare two N-bit binary values

- Equal-to or Not-equal-to

- Easiest to design

- Greater-than, Less-than, Greater-than-or-equal-to, etc.

- Require adders

#### Parity check/generate circuit

- Calculates even or odd parity over N bits of data

- Checks for good/bad parity (parity errors) on incoming data

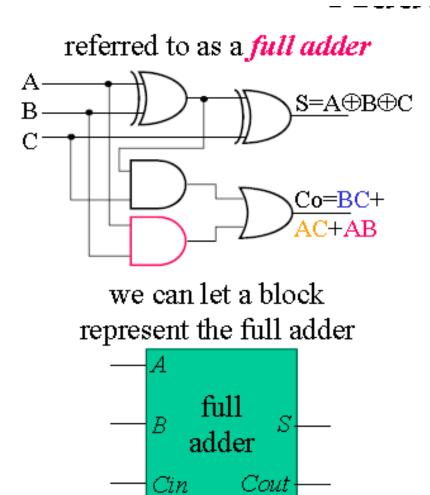

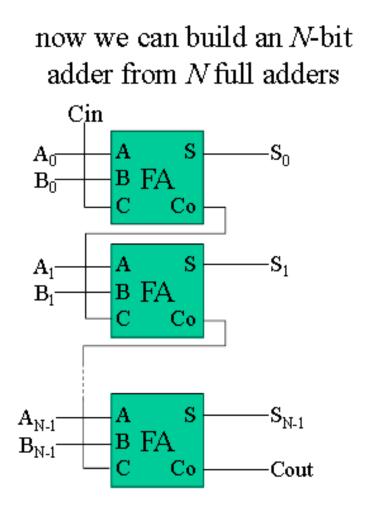

### Adder

- Consider *i*<sup>th</sup> column addition of 2 binary numbers (A and B)

- $A_i + B_i + Cin_i = Cout_i$  $+ Sum_i$

- Derive truth table

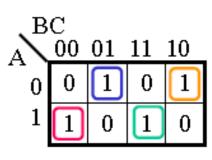

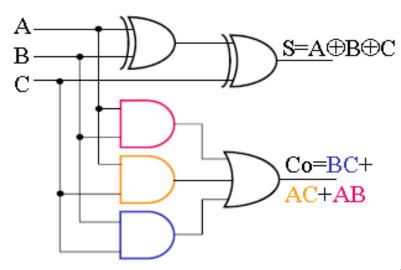

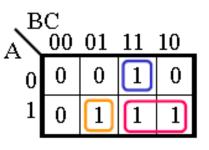

- Populate K-maps

- Obtain minimized SOPs

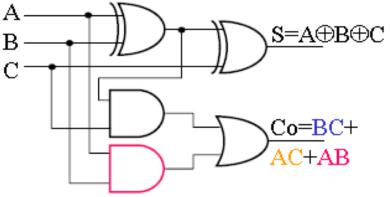

- Draw logic diagram

- Optimize with P&Ts

|   | Truth Table |     |    |   |  |  |  |

|---|-------------|-----|----|---|--|--|--|

| A | ΥB          | C C | Co | S |  |  |  |

| C | 0           | 0   | 0  | 0 |  |  |  |

| C | 0           | 1   | 0  | 1 |  |  |  |

| C | ) 1         | 0   | 0  | 1 |  |  |  |

| C | ) 1         | 1   | 1  | 0 |  |  |  |

| 1 | 0           | 0   | 0  | 1 |  |  |  |

| 1 | 0           | 1   | 1  | 0 |  |  |  |

| 1 | 1           | 0   | 1  | 0 |  |  |  |

| 1 | 1           | 1   | 1  | 1 |  |  |  |

$S=A^{B}C+ABC' + ABC' = A^{B}C + A$

Co=BC+AC+AB

### Adder

Taking advantage of common product terms between S and Co we see that we can use the XOR gate for A⊕B to reduce the gate count

$C_{0}=A'BC+AB'C+AB$ =C(A'B+AB')+AB $=C(A\oplus B)+AB$

### Adder